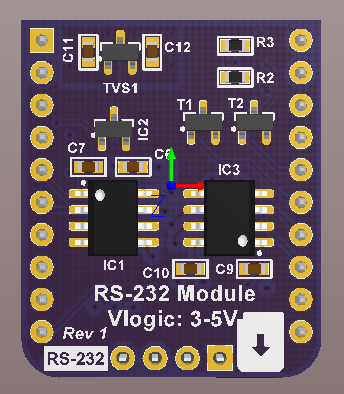

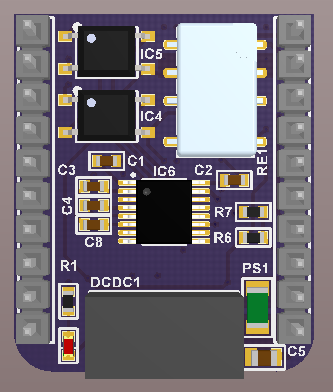

RS 232 Module

Schematics can be found here.

- Module ID: 5

- Fully isolated power and signals

- Outputs can be disconnected with a relay

- Two channels that can be set to TX or RX independently with CTRL pins

- IN_A: OUT_A - Outgoing data on channel A

- IN_B: IN_A - Incoming data on channel A

- IN_C: SWITCH - a HIGH signal switches the output relay ON and connects the outputs to the connector

- IN_D: ID - Used to set the module ID

- IN_E: CTRL_B - A HIGH signal sets channel B to an output and a LOW signal sets it to an input

- IN_F: CTRL_A - A HIGH signal sets channel A to an output and a LOW signal sets it to an input

- IN_G: OUT_B - Outgoing data on channel B

- IN_H: IN_B - Incoming data on channel B

- OUT_A: 5V isolated

- OUT_B: GND isolated

- OUT_C: CH_A_SWITCHED - The switched channel A pin, RS-232 compatible

- OUT_D: CH_B_SWITCHED - The switched channel B pin, RS-232 compatible

- RS-232

The board is 4 layer, 23.5x28 mm.

Homepage

Pictures

GUI Mockup

Contact

Version 2:

ui-processor-rtos

fpga-config-mcu

fpga-config-over-uart

Version 1:

freertos-serial-monitor

freertos-serial-monitor lcd test

Simple GUI:

General

GUIObject

GUIButton

GUILabel

GUIStaticTextBox

GUIAlertBox

GUIButtonGridBox

GUIButtonList

GUIInfoBox

Tasks:

LCD Task Message

LCD:

LCD ER-TFT070-4

LCD ER-TFTM070-5

LCD HY070CTP-HD

LCD HY101CTP-HD

LCD YL070MY01

Touch Controller

Measurements:

STM32 GPIO Speed

FT5206 Waveform Capture

Version 2:

Revision 2 Mockup

Module IDs

Boards:

Connection Board

UI Processor Board

Data Processor Board

Isolated Power Module

LCD Board

Modules:

1. GPIO Module

3. CAN Module

5. RS-232 Module

15. nRF24L01 Module

Future Module Ideas

FPGA:

FPGA Main Blocks

FPGA Communication

FPGA UART

FPGA GPIO

FPGA Timestamp

FPGA SDRAM

FPGA PLL

[FPGA ID Reader](https://github.com/hampussandberg/HexConnect/wiki/FPGA-ID Reader)

FPGA LVDS

FPGA Monitor

FPGA Tips and Tricks

Learning Quartus II

Version 1:

Requirement Specification

Hardware Design

Hardware Rev 1 Fixes