Implementation of a SPI master component in VHDL.

The component controls the communication between one SPI master and one SPI slave device. It generates the clock signal (SCLK) and the data (MOSI) signals, and reads the incoming data from the MISO signal line. The chip select signal is not generated by this component. The user has to make sure the chip select is set according to the slaves requirements.

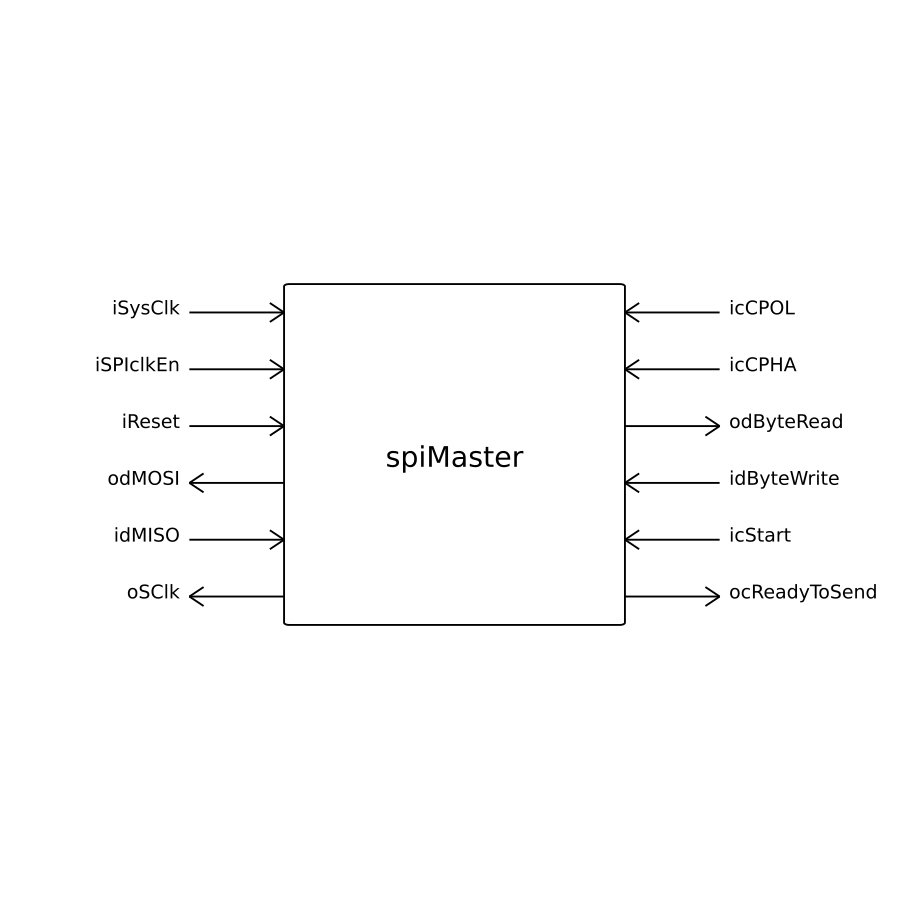

The image shows all the available signals.

| Signal Name | Length | Direction | Description |

|---|---|---|---|

| iSysClk | 1 | IN | System Clock Signal |

| iSPIclkEN | 1 | IN | spi clock enable signal (related to iSysClk) |

| iReset | 1 | IN | clock synchronous, active high reset signal |

| odMOSI | 1 | OUT | SPI MOSI signal |

| idMISO | 1 | IN | SPI MISO signal |

| oSclk | 1 | OUT | SPI Clock signal |

| icCPOL | 1 | IN | icCPOL and icCPHA set the SPI Mode, refer to SPI documentation |

| icCPHA | 1 | IN | icCPOL and icCPHA set the SPI Mode, refer to SPI documentation |

| odByteRead | 8 | OUT | Data read from the SPI MISO line. Size according to GEN_DataLength |

| idByteWrite | 8 | IN | Data written to the SPI MOSI line. Size according to GEN_DataLength |

| icStart | 1 | IN | Start the transfer |

| ocReadyToSend | 1 | OUT | Active high ready signal. When high the spiMaster is ready for the next transfer or has finished a transfer and odByteRead is valid. |

One Generic (GEN_DataLength) is available to set the number of transfer bits per action.

The input clock to the spiMaster has to be twice the wanted SPI clock frequency; either by applying it directly via iSysClk or via iSPIclkEn as an iSysClk aligned clock-enable signal.

For more information look at the doxygen documentation or the comments within the VHDL file.

You can contribute to this project in different ways:

- find bugs and provide bug reports through githubs issue system

- find bugs and provide solutions as pull requests through github

- you want to actively improve the project and get access to our gerrit instance

For the last two ways just send an email to mailto:dmeyer@hsu-hh.de.

The SPI-Master project is licensed under GPLv2.