Read the articles...

We're porting the NXP i.MX RT EHCI USB Driver from Apache NuttX RTOS to PinePhone and Allwinner A64...

To add the PinePhone USB Driver to our NuttX Project...

cd nuttx/arch/arm64/src/a64

git submodule add https://github.com/lupyuen/pinephone-nuttx-usb

ln -s pinephone-nuttx-usb/a64_ehci.c .

ln -s pinephone-nuttx-usb/a64_ehci.h .

ln -s pinephone-nuttx-usb/a64_usbhost.c .

pushd hardware

ln -s ../pinephone-nuttx-usb/a64_usbotg.h .

popdAdd the USB Driver to Kconfig, Makefile and PinePhone Bringup...

Configure the NuttX Build...

tools/configure.sh pinephone:lvgl

make menuconfigSelect these options in menuconfig...

-

Enable "Build Setup > Debug Options > USB Debug Features > USB Error, Warninigs and Info"

And "Battery-related Debug Features > Battery Error, Warnings and Info"

-

Enable "System Type > Allwinner A64 Peripheral Selection > USB EHCI"

-

Enable "RTOS Features > Work queue support > Low priority (kernel) worker thread"

-

Enable "Device Drivers > USB Host Driver Support"

-

Enable "Device Drivers > USB Host Driver Support > USB Hub Support"

Let's boot the NuttX USB EHCI Driver on PinePhone...

When PinePhone boots the NuttX USB EHCI Driver, it halts with an Assertion Failure...

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: chip/a64_ehci.c:4996 task: nsh_main 0x4008b0d0

Here's the assertion, which says that the a64_qh_s struct must be aligned to 32 bytes...

pinephone-nuttx-usb/a64_ehci.c

Line 4996 in b80499b

Size of the a64_qh_s struct is 72 bytes...

sizeof(struct a64_qh_s)=72

Which isn't aligned to 32 bytes...

pinephone-nuttx-usb/a64_ehci.c

Lines 186 to 200 in b80499b

Because it contains a 64-bit pointer epinfo...

pinephone-nuttx-usb/a64_ehci.c

Line 197 in b80499b

How has a64_qh_s changed for 32-bit platforms vs 64-bit platforms?

On 32-bit platforms: a64_qh_s was previously 64 bytes. (48 + 4 + 4 + 8)

On 64-bit platforms: a64_qh_s is now 72 bytes. (48 + 8 + 4 + 8, round up for 4-byte alignment)

In the EHCI Driver we need to align a64_qh_s to 32 bytes. So we pad a64_qh_s from 72 bytes to 96 bytes...

uint8_t pad2[96 - 72]; // TODO: Pad from 72 to 96 bytes for 64-bit platformLike this...

pinephone-nuttx-usb/a64_ehci.c

Lines 190 to 202 in 2e1f9ab

Which fixes the Assertion Failure.

What about other structs?

To be safe, we verified that the other Struct Sizes are still valid for 64-bit platforms...

pinephone-nuttx-usb/a64_ehci.c

Lines 4999 to 5004 in 2e1f9ab

Here are the Struct Sizes...

a64_ehci_initialize: sizeof(struct a64_qh_s)=72

a64_ehci_initialize: sizeof(struct a64_qtd_s)=32

a64_ehci_initialize: sizeof(struct ehci_itd_s)=64

a64_ehci_initialize: sizeof(struct ehci_sitd_s)=28

a64_ehci_initialize: sizeof(struct ehci_qtd_s)=32

a64_ehci_initialize: sizeof(struct ehci_overlay_s)=32

a64_ehci_initialize: sizeof(struct ehci_qh_s)=48

a64_ehci_initialize: sizeof(struct ehci_fstn_s)=8

We need to fix this typo in NuttX: SIZEOF_EHCI_OVERLAY is defined twice...

https://github.com/apache/nuttx/blob/master/include/nuttx/usb/ehci.h#L955-L974

The NuttX USB EHCI Driver fails with a timeout when booting on PinePhone...

a64_usbhost_initialize: TODO: a64_clockall_usboh3

a64_usbhost_initialize: TODO: switch off USB bus power

a64_usbhost_initialize: TODO: Setup pins, with power initially off

usbhost_registerclass: Registering class:0x40124838 nids:2

EHCI Initializing EHCI Stack

a64_ehci_initialize: TODO: a64_clockall_usboh3

a64_ehci_initialize: TODO: Reset the controller from the OTG peripheral

a64_ehci_initialize: TODO: Program the controller to be the USB host controller

a64_printreg: 01c1b010<-00000000

a64_printreg: 01c1b014->00000000

EHCI ERROR: Timed out waiting for HCHalted. USBSTS: 000000

EHCI ERROR: a64_reset failed: 110

a64_usbhost_initialize: ERROR: a64_ehci_initialize failed

The timeout happens while waiting for the USB Controller to Halt...

pinephone-nuttx-usb/a64_ehci.c

Lines 4831 to 4917 in 2e1f9ab

What are 01c1 b010 and 01c1 b014?

01c1 b000 is the Base Address of the USB EHCI Controller on Allwinner A64. (See this)

01c1 b010 is the USB Command Register USBCMD. (Page 18)

01c1 b014 is the USB Status Register USBSTS. (Page 21)

a64_printreg: 01c1b010<-00000000

a64_printreg: 01c1b014->00000000

According the log, the driver wrote Command 0 (Stop) to USB Command Register USBCMD. Which will Halt the USB Controller.

Then we read USB Status Register USBSTS. This returns 0, which means that the USB Controller has NOT been halted. (HCHalted = 0)

That's why the USB Driver failed: It couldn't Halt the USB Controller at startup.

Why?

Probably because we haven't powered on the USB Controller? According to the log...

a64_usbhost_initialize: TODO: a64_clockall_usboh3

a64_usbhost_initialize: TODO: switch off USB bus power

a64_usbhost_initialize: TODO: Setup pins, with power initially off

a64_ehci_initialize: TODO: a64_clockall_usboh3

a64_ehci_initialize: TODO: Reset the controller from the OTG peripheral

a64_ehci_initialize: TODO: Program the controller to be the USB host controller

And maybe we need to init the USB PHY (Physical Layer)?

How do we power on the USB Controller?

Let's check the U-Boot source code...

Let's find the PinePhone USB Driver in the U-Boot Bootloader, to understand how it powers on the USB Controller.

When we search for PinePhone in the Source Code of the U-Boot Bootloader, we find this Build Configuration: pinephone_defconfig

CONFIG_DEFAULT_DEVICE_TREE="sun50i-a64-pinephone-1.2"

Which refers to this PinePhone Device Tree: sun50i-a64-pinephone-1.2.dts

#include "sun50i-a64-pinephone.dtsi"

Which includes another PinePhone Device Tree: sun50i-a64-pinephone.dtsi

#include "sun50i-a64.dtsi"

#include "sun50i-a64-cpu-opp.dtsi"

...

&ehci0 { status = "okay"; };

&ehci1 { status = "okay"; };

&usb_otg {

dr_mode = "peripheral";

status = "okay";

};

&usb_power_supply { status = "okay"; };

&usbphy { status = "okay"; };

Which includes this Allwinner A64 Device Tree: sun50i-a64.dtsi

usb_otg: usb@1c19000 {

compatible = "allwinner,sun8i-a33-musb";

reg = <0x01c19000 0x0400>;

clocks = <&ccu CLK_BUS_OTG>;

resets = <&ccu RST_BUS_OTG>;

interrupts = <GIC_SPI 71 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "mc";

phys = <&usbphy 0>;

phy-names = "usb";

extcon = <&usbphy 0>;

dr_mode = "otg";

status = "disabled";

};

usbphy: phy@1c19400 {

compatible = "allwinner,sun50i-a64-usb-phy";

reg =

<0x01c19400 0x14>,

<0x01c1a800 0x4>,

<0x01c1b800 0x4>;

reg-names =

"phy_ctrl",

"pmu0",

"pmu1";

clocks =

<&ccu CLK_USB_PHY0>,

<&ccu CLK_USB_PHY1>;

clock-names =

"usb0_phy",

"usb1_phy";

resets =

<&ccu RST_USB_PHY0>,

<&ccu RST_USB_PHY1>;

reset-names =

"usb0_reset",

"usb1_reset";

status = "disabled";

#phy-cells = <1>;

};

ehci0: usb@1c1a000 {

compatible = "allwinner,sun50i-a64-ehci", "generic-ehci";

reg = <0x01c1a000 0x100>;

interrupts = <GIC_SPI 72 IRQ_TYPE_LEVEL_HIGH>;

clocks =

<&ccu CLK_BUS_OHCI0>,

<&ccu CLK_BUS_EHCI0>,

<&ccu CLK_USB_OHCI0>;

resets =

<&ccu RST_BUS_OHCI0>,

<&ccu RST_BUS_EHCI0>;

phys = <&usbphy 0>;

phy-names = "usb";

status = "disabled";

};

ehci1: usb@1c1b000 {

compatible = "allwinner,sun50i-a64-ehci", "generic-ehci";

reg = <0x01c1b000 0x100>;

interrupts = <GIC_SPI 74 IRQ_TYPE_LEVEL_HIGH>;

clocks =

<&ccu CLK_BUS_OHCI1>,

<&ccu CLK_BUS_EHCI1>,

<&ccu CLK_USB_OHCI1>;

resets =

<&ccu RST_BUS_OHCI1>,

<&ccu RST_BUS_EHCI1>;

phys = <&usbphy 1>;

phy-names = "usb";

status = "disabled";

};

Which says that the USB Drivers are...

-

EHCI0 and EHCI1 (Enhanced Host Controller Interface): "allwinner,sun50i-a64-ehci", "generic-ehci"

-

USB OTG (On-The-Go): "allwinner,sun8i-a33-musb"

-

USB PHY (Physical Layer): "allwinner,sun50i-a64-usb-phy"

Why so many USB drivers? Let's talk about it...

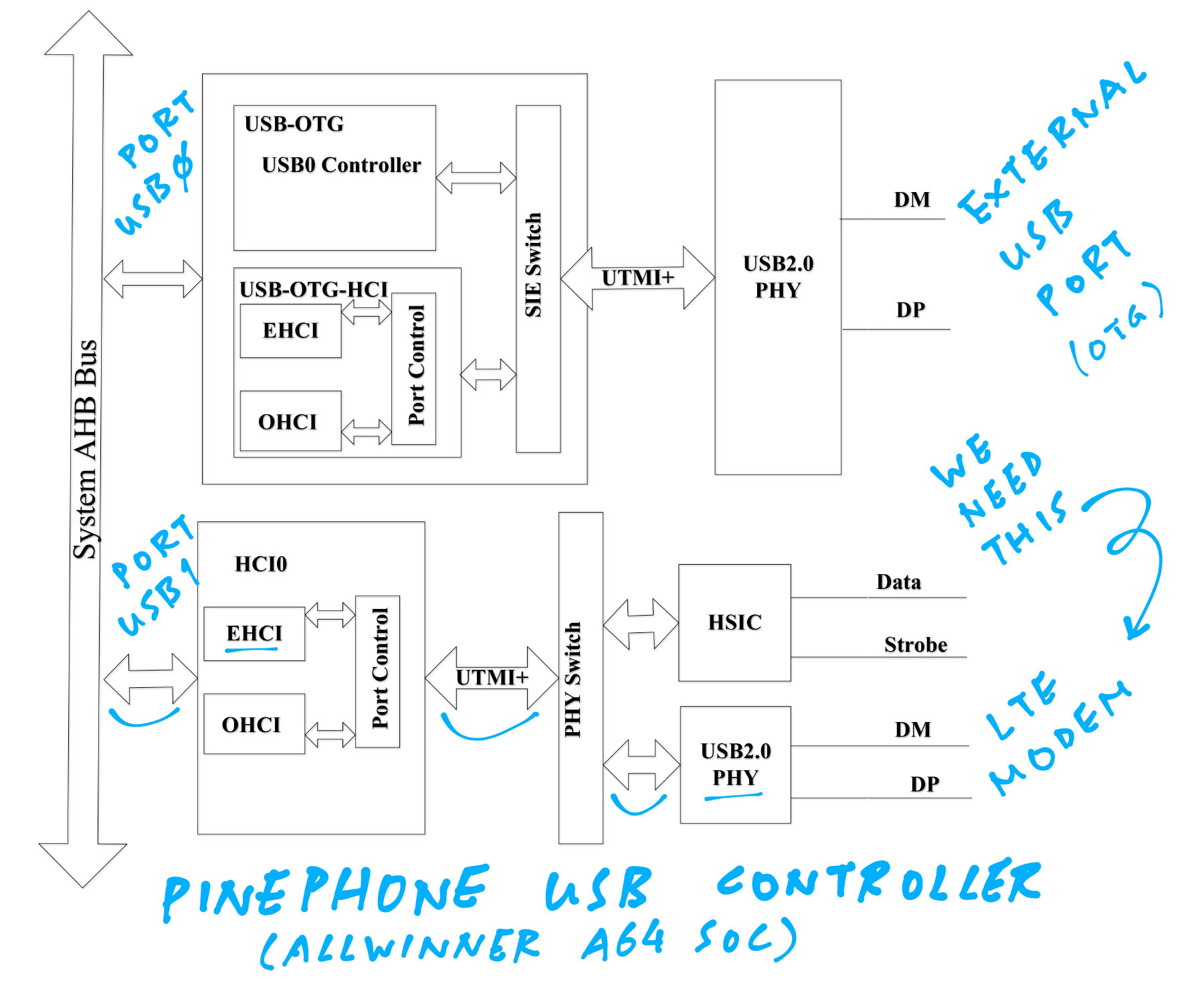

According to the USB Controller Block Diagram in Allwinner A64 User Manual (Page 583)...

There are two USB Ports in Allwinner A64: USB0 and USB1...

-

Port USB0 is exposed as the External USB Port on PinePhone

-

Port USB1 is connected to the Internal LTE Modem

| USB Port | Alternate Name | Base Address |

|---|---|---|

| Port USB0 | USB-OTG-EHCI / OHCI | 0x01C1 A000 (USB_HCI0) |

| Port USB1 | USB-EHCI0 / OHCI0 | 0x01C1 B000 (USB_HCI1) |

(Port USB0 Base Address isn't documented, but it appears in the Memory Mapping (Page 73) of the Allwinner A64 User Manual)

-

Only Port USB0 supports USB On-The-Go (OTG). Which means if we connect PinePhone to a computer, it will appear as a USB Drive. (Assuming the right drivers are started)

(That's why Port USB0 is exposed as the External USB Port on PinePhone)

-

Ports USB0 and USB1 both support Enhanced Host Controller Interface (EHCI). Which will work only as a USB Host (not USB Device)

Today we'll talk only about Port USB1 (EHCI / Non-OTG), since it's connected to the LTE Modem.

Earlier we searched for the USB Drivers for PinePhone and found these...

-

EHCI0 and EHCI1 (Enhanced Host Controller Interface):

-

USB PHY (Physical Layer):

We disregard the USB OTG Driver because we're only interested in the EHCI Driver (Non-OTG) for PinePhone.

The USB PHY Driver handles the Physical Layer (physical wires) that connect to the USB Controller.

To power on the USB Controller ourselves, let's look inside the USB PHY Driver: sun4i_usb_phy_init

static int sun4i_usb_phy_init(struct phy *phy)

{

struct sun4i_usb_phy_data *data = dev_get_priv(phy->dev);

struct sun4i_usb_phy_plat *usb_phy = &data->usb_phy[phy->id];

u32 val;

int ret;

ret = clk_enable(&usb_phy->clocks);

if (ret) {

dev_err(phy->dev, "failed to enable usb_%ldphy clock\n",

phy->id);

return ret;

}In the code above we enable the USB Clocks. We'll explain here...

Then we deassert the USB Reset...

ret = reset_deassert(&usb_phy->resets);

if (ret) {

dev_err(phy->dev, "failed to deassert usb_%ldreset reset\n",

phy->id);

return ret;

}We'll explain the USB Reset here...

TODO: Is PMU is needed for PinePhone Port USB1? If PMU is not needed, we skip this part...

// `hci_phy_ctl_clear` is `PHY_CTL_H3_SIDDQ`, which is `1 << 1`

// https://github.com/lupyuen/pinephone-nuttx-usb#usb-controller-configuration

if (usb_phy->pmu && data->cfg->hci_phy_ctl_clear) {

val = readl(usb_phy->pmu + REG_HCI_PHY_CTL);

val &= ~data->cfg->hci_phy_ctl_clear;

writel(val, usb_phy->pmu + REG_HCI_PHY_CTL);

}(FYI: PinePhone Port USB0 is connected to the PMIC, according to PinePhone Schematic Page 6)

PinePhone is sun50i_a64_phy, so we skip this part...

// Skip this part because PinePhone is `sun50i_a64_phy`

if (data->cfg->type == sun8i_a83t_phy ||

data->cfg->type == sun50i_h6_phy) {

if (phy->id == 0) {

val = readl(data->base + data->cfg->phyctl_offset);

val |= PHY_CTL_VBUSVLDEXT;

val &= ~PHY_CTL_SIDDQ;

writel(val, data->base + data->cfg->phyctl_offset);

}PinePhone is sun50i_a64_phy, so we run this instead...

} else {

if (usb_phy->id == 0)

sun4i_usb_phy_write(phy, PHY_RES45_CAL_EN,

PHY_RES45_CAL_DATA,

PHY_RES45_CAL_LEN);

/* Adjust PHY's magnitude and rate */

sun4i_usb_phy_write(phy, PHY_TX_AMPLITUDE_TUNE,

PHY_TX_MAGNITUDE | PHY_TX_RATE,

PHY_TX_AMPLITUDE_LEN);

/* Disconnect threshold adjustment */

sun4i_usb_phy_write(phy, PHY_DISCON_TH_SEL,

data->cfg->disc_thresh, PHY_DISCON_TH_LEN);

}Which will...

-

Set PHY_RES45_CAL (TODO: What's this?)

-

Set USB PHY Magnitude and Rate

-

Disconnect USB PHY Threshold Adjustment

As explained here...

TODO: Is usb_phy->id set to 1 for USB Port 1?

Assume CONFIG_USB_MUSB_SUNXI is undefined. So we skip this part...

#ifdef CONFIG_USB_MUSB_SUNXI

// Skip this part because `CONFIG_USB_MUSB_SUNXI` is undefined

/* Needed for HCI and conflicts with MUSB, keep PHY0 on MUSB */

if (usb_phy->id != 0)

sun4i_usb_phy_passby(phy, true);

/* Route PHY0 to MUSB to allow USB gadget */

if (data->cfg->phy0_dual_route)

sun4i_usb_phy0_reroute(data, true);CONFIG_USB_MUSB_SUNXI is undefined, so we run this instead...

#else

sun4i_usb_phy_passby(phy, true);

/* Route PHY0 to HCI to allow USB host */

if (data->cfg->phy0_dual_route)

sun4i_usb_phy0_reroute(data, false);

#endif

return 0;

}Which will...

-

Enable USB PHY Bypass

-

Route USB PHY0 to EHCI (instead of Mentor Graphics OTG MUSB)

sun4i_usb_phy_passby and sun4i_usb_phy0_reroute are defined here...

What's CONFIG_USB_MUSB_SUNXI?

CONFIG_USB_MUSB_SUNXI enables support for the Mentor Graphics OTG / DRC USB Controller...

config USB_MUSB_SUNXI

bool "Enable sunxi OTG / DRC USB controller"

depends on ARCH_SUNXI

select USB_MUSB_PIO_ONLY

default y

---help---

Say y here to enable support for the sunxi OTG / DRC USB controller

used on almost all sunxi boards.

We assume CONFIG_USB_MUSB_SUNXI is disabled because we won't be using USB OTG for NuttX (yet).

Earlier we looked at the Source Code for the USB PHY Driver for PinePhone...

And we saw this code that will enable the USB Clocks: sun4i_usb_phy_init

ret = clk_enable(&usb_phy->clocks);clk_enable is explained here...

What's usb_phy->clocks?

According to the PinePhone Device Tree, the USB Clocks are...

-

usb0_phy: CLK_USB_PHY0

-

usb1_phy: CLK_USB_PHY1

-

EHCI0: CLK_BUS_OHCI0, CLK_BUS_EHCI0, CLK_USB_OHCI0

-

EHCI1: CLK_BUS_OHCI1, CLK_BUS_EHCI1, CLK_USB_OHCI1

What are the values of the above USB Clocks?

The USB Clocks are defined in clock/sun50i-a64-ccu.h...

#define CLK_BUS_EHCI0 42

#define CLK_BUS_EHCI1 43

#define CLK_BUS_OHCI0 44

#define CLK_BUS_OHCI1 45

#define CLK_USB_PHY0 86

#define CLK_USB_PHY1 87

#define CLK_USB_OHCI0 91

#define CLK_USB_OHCI1 93Which are consistent with the values in the PinePhone JumpDrive Device Tree: sun50i-a64-pinephone-1.2.dts

The Allwinner A64 Register Addresses for USB Clocks are defined here...

Here's the definition of USB Clocks in our U-Boot Device Tree: sun50i-a64.dtsi

usbphy: phy@1c19400 {

reg =

<0x01c19400 0x14>,

<0x01c1a800 0x4>,

<0x01c1b800 0x4>;

reg-names =

"phy_ctrl",

"pmu0",

"pmu1";

clocks =

<&ccu CLK_USB_PHY0>,

<&ccu CLK_USB_PHY1>;

clock-names =

"usb0_phy",

"usb1_phy";

...

ehci0: usb@1c1a000 {

reg = <0x01c1a000 0x100>;

clocks =

<&ccu CLK_BUS_OHCI0>,

<&ccu CLK_BUS_EHCI0>,

<&ccu CLK_USB_OHCI0>;

...

ehci1: usb@1c1b000 {

reg = <0x01c1b000 0x100>;

clocks =

<&ccu CLK_BUS_OHCI1>,

<&ccu CLK_BUS_EHCI1>,

<&ccu CLK_USB_OHCI1>;

resets =

<&ccu RST_BUS_OHCI1>,

<&ccu RST_BUS_EHCI1>;

(CCU means Clock Control Unit)

What are the USB PHY Reg Values from above?

usbphy: phy@1c19400 {

reg =

<0x01c19400 0x14>,

<0x01c1a800 0x4>,

<0x01c1b800 0x4>;

reg-names =

"phy_ctrl",

"pmu0",

"pmu1";

According to the Allwinner A64 User Manual (Memory Mapping, Page 73)...

-

phy_ctrl:

0x01c19400(Offset0x14)Belongs to USB-OTG-Device (USB Port 0)

-

pmu0:

0x01c1a800(Offset0x4)Belongs to USB-OTG-EHCI (USB Port 0)

-

pmu1:

0x01c1b800(Offset0x4)Belongs to USB-EHCI0 (USB Port 1)

Earlier we looked at the Source Code for the USB PHY Driver for PinePhone...

And we saw this code that will deassert the USB Reset: sun4i_usb_phy_init

ret = reset_deassert(&usb_phy->resets);reset_deassert is explained here...

What's usb_phy->resets?

According to the PinePhone Device Tree, the USB Resets are...

-

usb0_reset: RST_USB_PHY0

-

usb1_reset: RST_USB_PHY1

-

EHCI0: RST_BUS_OHCI0, RST_BUS_EHCI0

-

EHCI1: RST_BUS_OHCI1, RST_BUS_EHCI1

What are the values of the USB Resets?

The USB Resets are defined in reset/sun50i-a64-ccu.h...

#define RST_USB_PHY0 0

#define RST_USB_PHY1 1

#define RST_BUS_EHCI0 19

#define RST_BUS_EHCI1 20

#define RST_BUS_OHCI0 21

#define RST_BUS_OHCI1 22Which are consistent with the values in the PinePhone JumpDrive Device Tree: sun50i-a64-pinephone-1.2.dts

The Allwinner A64 Register Addresses for USB Resets are defined here...

Here's the definition of USB Resets in our U-Boot Device Tree: sun50i-a64.dtsi

usbphy: phy@1c19400 {

resets =

<&ccu RST_USB_PHY0>,

<&ccu RST_USB_PHY1>;

reset-names =

"usb0_reset",

"usb1_reset";

...

ehci0: usb@1c1a000 {

resets =

<&ccu RST_BUS_OHCI0>,

<&ccu RST_BUS_EHCI0>;

...

ehci1: usb@1c1b000 {

resets =

<&ccu RST_BUS_OHCI1>,

<&ccu RST_BUS_EHCI1>;

Earlier we saw this code that will enable the USB Clocks: sun4i_usb_phy_init

ret = clk_enable(&usb_phy->clocks);(USB Clocks usb_phy->clocks are defined here)

clk_enable calls sunxi_set_gate

Which A64 Registers will our NuttX USB Driver set?

Our NuttX USB Driver will set the CCU Registers, defined in Allwinner A64 User Manual, Page 81.

(CCU Base Address is 0x01C2 0000)

Based on the USB Clocks usb_phy->clocks, our NuttX USB Driver will set the following CCU Registers: clk_a64.c

static const struct ccu_clk_gate a64_gates[] = {

[CLK_BUS_EHCI0] = GATE(0x060, BIT(24)),

[CLK_BUS_EHCI1] = GATE(0x060, BIT(25)),

[CLK_BUS_OHCI0] = GATE(0x060, BIT(28)),

[CLK_BUS_OHCI1] = GATE(0x060, BIT(29)),

[CLK_USB_PHY0] = GATE(0x0cc, BIT(8)),

[CLK_USB_PHY1] = GATE(0x0cc, BIT(9)),

[CLK_USB_OHCI0] = GATE(0x0cc, BIT(16)),

[CLK_USB_OHCI1] = GATE(0x0cc, BIT(17)),So to enable the USB Clock CLK_BUS_EHCI0, we'll set Bit 24 of the CCU Register at 0x060 + 0x01C2 0000.

This will be similar to setting SCLK_GATING of DE_CLK_REG as described here...

TODO: What about OHCI1_12M_SRC_SEL, OHCI0_12M_SRC_SEL? (Allwinner A64 User Manual Page 113)

Earlier we saw this code that will deassert the USB Reset: sun4i_usb_phy_init

ret = reset_deassert(&usb_phy->resets);(USB Resets usb_phy->resets are defined here)

reset_deassert calls...

-

rst_deassert, which calls... -

sunxi_reset_deassert, which calls...

Which A64 Registers will our NuttX USB Driver set?

Our NuttX USB Driver will set the CCU Registers, defined in Allwinner A64 User Manual, Page 81.

(CCU Base Address is 0x01C2 0000)

Based on the USB Resets usb_phy->resets, our NuttX USB Driver will set the following CCU Registers: clk_a64.c

static const struct ccu_reset a64_resets[] = {

[RST_USB_PHY0] = RESET(0x0cc, BIT(0)),

[RST_USB_PHY1] = RESET(0x0cc, BIT(1)),

[RST_BUS_EHCI0] = RESET(0x2c0, BIT(24)),

[RST_BUS_EHCI1] = RESET(0x2c0, BIT(25)),

[RST_BUS_OHCI0] = RESET(0x2c0, BIT(28)),

[RST_BUS_OHCI1] = RESET(0x2c0, BIT(29)),So to deassert the USB Reset RST_USB_PHY0, we'll set Bit 0 of the CCU Register at 0x0cc + 0x01C2 0000.

This will be similar to setting DE_RST of BUS_SOFT_RST_REG1 as described here...

Earlier the NuttX USB EHCI Driver fails during PinePhone startup...

Then we discovered how the U-Boot Bootloader enables the USB Clocks and deasserts the USB Resets...

So we do the same for NuttX. And now the NuttX EHCI Driver starts OK on PinePhone yay! 🎉

This is how we enable the USB Clocks and deassert the USB Resets on PinePhone...

pinephone-nuttx-usb/a64_usbhost.c

Lines 118 to 279 in 0e1632e

Here's the log...

a64_usbhost_clk_enable: CLK_USB_PHY0

set_bit: 0x1c200cc Bit 8

a64_usbhost_clk_enable: CLK_USB_PHY1

set_bit: 0x1c200cc Bit 9

a64_usbhost_clk_enable: CLK_BUS_OHCI0

set_bit: 0x1c20060 Bit 28

a64_usbhost_clk_enable: CLK_BUS_EHCI0

set_bit: 0x1c20060 Bit 24

a64_usbhost_clk_enable: CLK_USB_OHCI0

set_bit: 0x1c200cc Bit 16

a64_usbhost_clk_enable: CLK_BUS_OHCI1

set_bit: 0x1c20060 Bit 29

a64_usbhost_clk_enable: CLK_BUS_EHCI1

set_bit: 0x1c20060 Bit 25

a64_usbhost_clk_enable: CLK_USB_OHCI1

set_bit: 0x1c200cc Bit 17

a64_usbhost_reset_deassert: RST_USB_PHY0

set_bit: 0x1c200cc Bit 0

a64_usbhost_reset_deassert: RST_USB_PHY1

set_bit: 0x1c200cc Bit 1

a64_usbhost_reset_deassert: RST_BUS_OHCI0

set_bit: 0x1c202c0 Bit 28

a64_usbhost_reset_deassert: RST_BUS_EHCI0

set_bit: 0x1c202c0 Bit 24

a64_usbhost_reset_deassert: RST_BUS_OHCI1

set_bit: 0x1c202c0 Bit 29

a64_usbhost_reset_deassert: RST_BUS_EHCI1

set_bit: 0x1c202c0 Bit 25

This log above shows NuttX enabling the USB Clocks and deasserting the USB Resets for...

-

USB PHY0 and USB PHY1

-

EHCI0 and OHCI0

-

EHCI1 and OHCI1

(Yeah this looks excessive. We probably need only USB PHY1, EHCI1 and OHCI1)

Then the NuttX EHCI Driver starts...

a64_usbhost_initialize: TODO: a64_clockall_usboh3

a64_usbhost_initialize: TODO: switch off USB bus power

a64_usbhost_initialize: TODO: Setup pins, with power initially off

usbhost_registerclass: Registering class:0x40124838 nids:2

a64_ehci_initialize: sizeof(struct a64_qh_s)=96

a64_ehci_initialize: sizeof(struct a64_qtd_s)=32

a64_ehci_initialize: sizeof(struct ehci_itd_s)=64

a64_ehci_initialize: sizeof(struct ehci_sitd_s)=28

a64_ehci_initialize: sizeof(struct ehci_qtd_s)=32

a64_ehci_initialize: sizeof(struct ehci_overlay_s)=32

a64_ehci_initialize: sizeof(struct ehci_qh_s)=48

a64_ehci_initialize: sizeof(struct ehci_fstn_s)=8

EHCI Initializing EHCI Stack

a64_ehci_initialize: TODO: a64_clockall_usboh3

a64_ehci_initialize: TODO: Reset the controller from the OTG peripheral

a64_ehci_initialize: TODO: Program the controller to be the USB host controller

a64_printreg: 01c1b010<-00000000

a64_printreg: 01c1b014->00001000

a64_printreg: 01c1b010->00000000

a64_printreg: 01c1b010<-00000002

a64_printreg: 01c1b010->00080b00

a64_ehci_initialize: TODO: Re-program the USB host controller

a64_printreg: 01c1b018<-00000000

a64_printreg: 01c1b014<-0000003f

EHCI HCIVERSION 1.00

a64_printreg: 01c1b004->00001101

EHCI nports=1, HCSPARAMS=1101

a64_printreg: 01c1b008->0000a026

EHCI HCCPARAMS=00a026

a64_printreg: 01c1b028<-40a87fa0

a64_printreg: 01c1b024<-40a95000

a64_printreg: 01c1b010->00080b00

a64_printreg: 01c1b010<-00080b30

a64_printreg: 01c1b010->00080b30

a64_printreg: 01c1b010<-00080b31

a64_printreg: 01c1b050->00000000

a64_printreg: 01c1b050<-00000001

a64_printreg: 01c1b014->00000000

a64_ehci_initialize: TODO: irq_attach

a64_printreg: 01c1b018<-00000037

a64_ehci_initialize: TODO: up_enable_irq

a64_ehci_initialize: TODO: a64_usbhost_vbusdrive

a64_printreg: 01c1b054->00001000

EHCI USB EHCI Initialized

NuttShell (NSH) NuttX-12.0.3

nsh>

The log above says that NuttX has successfully started the EHCI Controller. Yay!

EHCI HCIVERSION 1.00

EHCI nports=1, HCSPARAMS=1101

EHCI HCCPARAMS=00a026

EHCI USB EHCI Initialized

In the NuttX Log above, what are the values of the EHCI Registers?

Let's decode the values of the USB EHCI Registers, to make sure that PinePhone is returning the right values on NuttX...

-

EHCI Log begins with...

EHCI Initializing EHCI Stack a64_ehci_initialize: TODO: a64_clockall_usboh3 a64_ehci_initialize: TODO: Reset the controller from the OTG peripheral a64_ehci_initialize: TODO: Program the controller to be the USB host controllerThen we see the EHCI Registers and their values...

-

Write USBCMD: USB Command Register (EHCI Page 18)

(To halt the USB Controller)

Run / Stop (RS, Bit 0) = 0

- Halt the Host Controller

a64_printreg: 01c1b010<-00000000 -

Read USBSTS: USB Status Register (EHCI Page 21)

(To verify that USB Controller has been halted)

HCHalted (Bit 12) = 1

- Host Controller has halted

a64_printreg: 01c1b014->00001000 -

Read USBCMD: USB Command Register (EHCI Page 18)

(To verify that USB Controller has been halted)

Run / Stop (RS, Bit 0) = 0

- Host Controller has halted

a64_printreg: 01c1b010->00000000 -

Write USBCMD: USB Command Register (EHCI Page 18)

(To reset the USB Controller)

Host Controller Reset (HCRESET, Bit 1) = 1

- Reset the Host Controller

a64_printreg: 01c1b010<-00000002 -

Read USBCMD: USB Command Register (EHCI Page 18)

Asynchronous Schedule Park Mode Count (Bits 8-9) = 3 (default)

Asynchronous Schedule Park Mode Enable (Bit 11) = 1 (default)

Interrupt Threshold Control (Bits 16-23) = 8 (default)

- 8 micro-frames / 1 ms

a64_printreg: 01c1b010->00080b00 a64_ehci_initialize: TODO: Re-program the USB host controller -

Write USBINTR: USB Interrupt Enable Register (EHCI Page 22)

Disable all interrupts

a64_printreg: 01c1b018<-00000000 -

Write USBSTS: USB Status Register (EHCI Page 21)

USB Interrupt (USBINT, Bit 0) = 1 (Reset)

USB Error Interrupt (USBERRINT, Bit 1) = 1 (Reset)

Port Change Detect (Bit 2) = 1 (Reset)

Frame List Rollover (Bit 3) = 1 (Reset)

Host System Error (Bit 4) = 1 (Reset)

Interrupt on Async Advance (Bit 5) = 1 (Reset)

a64_printreg: 01c1b014<-0000003f EHCI HCIVERSION 1.00 -

Read HCSPARAMS: Structural Parameters (EHCI Page 14)

N_PORTS (Bits 0 to 3) = 1 (Number of physical downstream ports)

Number of Ports per Companion Controller (N_PCC, Bits 8 to 11) = 1

- Number of ports supported per companion host controller

Number of Companion Controller (N_CC, Bits 12 to 15) = 1

- Number of companion controllers

a64_printreg: 01c1b004->00001101 EHCI nports=1, HCSPARAMS=1101 -

Read HCCPARAMS: Capability Parameters (EHCI Page 15)

64-bit Addressing Capability (Bit 0) = 0

- 32-bit address memory pointers only

Programmable Frame List Flag (Bit 1) = 1

- System software can specify and use a smaller frame list

Asynchronous Schedule Part Capability (Bit 2) = 1

- Support park feature for high-speed queue heads in the Asynchronous Schedule

Isochronous Scheduling Threshold (Bits 4 to 7) = 2

EHCI Extended Capabilities Pointer (EECP, Bits 8 to 15) = 0xA0

a64_printreg: 01c1b008->0000a026 EHCI HCCPARAMS=00a026 -

Write ASYNCLISTADDR: Current Asynchronous List Address Register (EHCI Page 25)

Address of the next asynchronous queue head to be executed

a64_printreg: 01c1b028<-40a86fa0 -

Write PERIODICLISTBASE: Periodic Frame List Base Address Register (EHCI Page 24)

Beginning address of the Periodic Frame List in the system memory

a64_printreg: 01c1b024<-40a97000 -

Read USBCMD: Same as above

a64_printreg: 01c1b010->00080b00 -

Write USBCMD: USB Command Register (EHCI Page 18)

Periodic Schedule Enable (Bit 4) = 1

- Use the PERIODICLISTBASE register to access the Periodic Schedule

Asynchronous Schedule Enable (Bit 5) = 1

- Use the ASYNCLISTADDR register to access the Asynchronous Schedule

Asynchronous Schedule Park Mode Count (Bits 8-9) = 3 (default)

Asynchronous Schedule Park Mode Enable (Bit 11) = 1 (default)

Interrupt Threshold Control (Bits 16-23) = 8 (default)

- 8 micro-frames / 1 ms

a64_printreg: 01c1b010<-00080b30 -

Read USBCMD: Same as above

a64_printreg: 01c1b010->00080b30 -

Write USBCMD: Same as above, plus...

(To start the USB Controller)

Run / Stop (RS, Bit 0) = 1

- Start Host Controller

a64_printreg: 01c1b010<-00080b31 -

Read CONFIGFLAG: Configure Flag Register (EHCI Page 25)

Configure Flag (CF, Bit 0) = 0

- Route each port to an implementation dependent classic host controller

a64_printreg: 01c1b050->00000000 -

Write CONFIGFLAG: Configure Flag Register (EHCI Page 25)

Configure Flag (CF, Bit 0) = 1

- Route all ports to this host controller

a64_printreg: 01c1b050<-00000001 -

Read USBSTS: USB Status Register (EHCI Page 21)

(To verify that USB Controller has been started)

HCHalted (Bit 12) = 0

- Host Controller has started

a64_printreg: 01c1b014->00000000 a64_ehci_initialize: TODO: irq_attach -

Write USBINTR: USB Interrupt Enable Register

(To enable the USB Interrupts)

USB Interrupt Enable (Bit 0) = 1

USB Error Interrupt Enable (Bit 1) = 1

Port Change Interrupt Enable (Bit 2) = 1

Host System Error Enable (Bit 4) = 1

Interrupt on Async Advance Enable (Bit 5) = 1

a64_printreg: 01c1b018<-00000037 a64_ehci_initialize: TODO: up_enable_irq a64_ehci_initialize: TODO: a64_usbhost_vbusdrive -

Read PORTSC: Port Status and Control Register (EHCI Page 26)

Port Power (PP, Bit 12) = 1

- Host controller has port power control switches

a64_printreg: 01c1b054->00001000 EHCI USB EHCI Initialized

The above values look OK for PinePhone.

When we enable USB Hub Support and run ls, NuttX halts with an Assertion Failure...

NuttShell (NSH) NuttX-12.0.3

nsh> ls /dev

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: mm_heap/mm_malloc.c:200 task: nsh_main 0x4008b380

up_dump_register: stack = 0x4012e660

up_dump_register: x0: 0x4012e660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f3b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x40a8e218 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008ecc0 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a95608 x21: 0x400f392d

up_dump_register: x22: 0x0 x23: 0xc8

up_dump_register: x24: 0x400f1277 x25: 0x40125000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b328

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a97900

up_dump_register: SP_ELX: 0x40a97610

up_dump_register: TPIDR_EL0: 0x40a95608

up_dump_register: TPIDR_EL1: 0x40a95608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

Here's the Assertion Failure: mm/mm_heap/mm_malloc.c

FAR void *mm_malloc(FAR struct mm_heap_s *heap, size_t size) {

...

DEBUGASSERT((next->size & MM_ALLOC_BIT) != 0 &&

(next->size & MM_PREVFREE_BIT) != 0 &&

next->preceding == nodesize);TODO: What does this mean?

TODO: Enable Memory Allocation Log

TODO: Lookup the addresses in the Register Dump

How does NuttX enumerate USB Devices?

Let's figure out how NuttX will enumerate the LTE Modem on PinePhone.

At startup, a64_usbhost_initialize creates a thread for...

-

ehci_waiter, which calls....

-

a64_wait to wait for a USB Device to be connected...

-

But a64_wait blocks on a Semaphore

pscsem, waiting for a change in the Connection State of a Root Hub Port -

pcsemis signalled by a64_connect

TODO: Who calls a64_connect?

Let's assume a64_connect is called by the USB Interrupt Handler a64_ehci_interrupt.

If a64_wait is successful...

-

ehci_waiter will call...

-

a64_enumerate, which calls...

-

usbhost_enumerate, which calls...

-

usbhost_devdesc to print the USB Descriptor

Let's handle the USB Interrupt, so that a64_connect will be triggered to begin the above USB Enumeration...

How will we handle USB Interrupts for NuttX on PinePhone?

Here's the Interrupt Handler for the NuttX USB EHCI Driver...

We need to attach this Interrupt Handler to the USB Interrupt for PinePhone / Allwinner A64 SoC.

What's the USB IRQ for PinePhone?

According to the Allwinner A64 User Manual ("3.12: GIC", Page 212), the IRQ Numbers for USB are...

- USB-OTG: 103

- USB-OTG-EHCI: 104

- USB-OTG-OHCI: 105

- USB-EHCI0: 106

- USB-OHCI0: 107

We will only handle USB-EHCI0 (IRQ 106), since it's connected to the LTE Modem.

This is how we attach the USB Interrupt Handler a64_ehci_interrupt to IRQ 106...

pinephone-nuttx-usb/a64_ehci.c

Lines 5343 to 5351 in 409a6ed

But the USB Interrupt Handler is not triggered. Let's power on the LTE Modem...

How to power up PinePhone's LTE Modem?

Read the article...

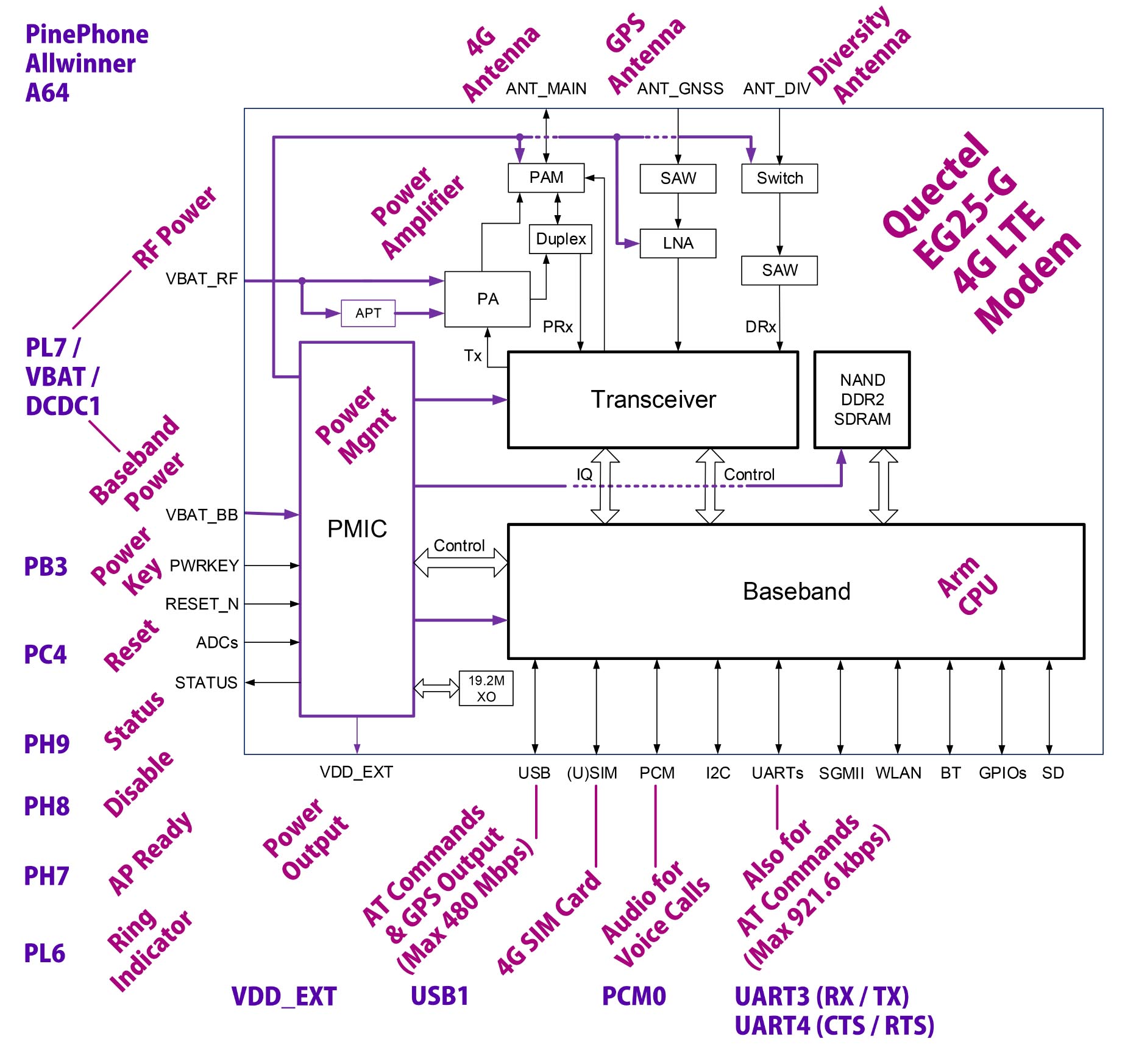

According to PinePhone Schematic Page 15, the LTE Modem is connected to...

-

Power DCDC1: From PMIC, 3.3V (See this)

-

Power VBAT: PL7 (4G-PWR-BAT) (See this)

-

Power VDD_EXT: From LTE Modem (EG25-G HW Guide Page 22)

-

Reset: BB-RESET (RESET_N) -> PC4-RESET-4G

-

Power Key: BB-PWRKEY (PWRKEY) -> PB3-PWRKEY-4G

-

Disable: BB-DISABLE (W_DISABLE#) -> PH8-DISABLE-4G

-

Status: PH9-STATUS

-

Ring Indicator: PMIC ALDO2 1.8V / PL6 (RI) (See this)

-

AP Ready: BB-AP-READY (AP_READY) -> PH7-AP-READY

Note: RESET_N and PWRKEY are High-Low Inverted when accessed through PinePhone’s GPIO Pins.

(LTE Modem Pins are explained in the next section)

So to power up PinePhone's LTE Modem, we need to...

-

Program PinePhone's Power Management Integrated Circuit (PMIC) to supply 3.3 V on DCDC1 (Like this)

We skip this because DCDC1 is already powered on.

-

Set PL7 to High to power on the RF Transceiver and Baseband Processor

-

Set PC4 to Low to deassert LTE Modem Reset

-

Set PH7 (AP-READY) to Low to wake up the modem

-

Set PB2 (DTR) to Low to wake up the modem

-

Wait 30 milliseconds for VBAT Power Supply to be stable

-

Toggle PB3 (Power Key) to start the LTE Modem, like this:

Set PB3 to High...

And wait 600 milliseconds...

Then set PB3 to Low.

-

Set PH8 to High to disable Airplane Mode

-

Read PH9 to check the LTE Modem Status:

PH9 goes from High to Low when the LTE Modem is ready, in 2.5 seconds.

-

UART and USB Interfaces will be operational in 13 seconds

The code looks like this: pinephone_bringup.c

// Init PinePhone LTE Modem

int pinephone_modem_init(void)

{

int ret;

// Read PH9 to check LTE Modem Status

#define STATUS (PIO_INPUT | PIO_PORT_PIOH | PIO_PIN9)

_info("Configure STATUS (PH9) for Input\n");

ret = a64_pio_config(STATUS);

DEBUGASSERT(ret == OK);

_info("Status=%d\n", a64_pio_read(STATUS));

// Set PL7 to High to Power On LTE Modem (4G-PWR-BAT)

#define P_OUTPUT (PIO_OUTPUT | PIO_PULL_NONE | PIO_DRIVE_MEDLOW | \

PIO_INT_NONE | PIO_OUTPUT_SET)

#define PWR_BAT (P_OUTPUT | PIO_PORT_PIOL | PIO_PIN7)

_info("Configure PWR_BAT (PL7) for Output\n");

ret = a64_pio_config(PWR_BAT);

DEBUGASSERT(ret >= 0);

_info("Set PWR_BAT (PL7) to High\n");

a64_pio_write(PWR_BAT, true);

_info("Status=%d\n", a64_pio_read(STATUS));

// Set PC4 to Low to Deassert LTE Modem Reset (BB-RESET / RESET_N)

#define RESET_N (P_OUTPUT | PIO_PORT_PIOC | PIO_PIN4)

_info("Configure RESET_N (PC4) for Output\n");

ret = a64_pio_config(RESET_N);

DEBUGASSERT(ret >= 0);

_info("Set RESET_N (PC4) to Low\n");

a64_pio_write(RESET_N, false);

_info("Status=%d\n", a64_pio_read(STATUS));

// Set AP-READY (PH7) to Low to wake up modem

#define AP_READY (P_OUTPUT | PIO_PORT_PIOH | PIO_PIN7)

_info("Configure AP-READY (PH7) for Output\n");

ret = a64_pio_config(AP_READY);

DEBUGASSERT(ret >= 0);

_info("Set AP-READY (PH7) to Low to wake up modem\n");

a64_pio_write(AP_READY, false);

_info("Status=%d\n", a64_pio_read(STATUS));

// Set DTR (PB2) to Low to wake up modem

#define DTR (P_OUTPUT | PIO_PORT_PIOB | PIO_PIN2)

_info("Configure DTR (PB2) for Output\n");

ret = a64_pio_config(DTR);

DEBUGASSERT(ret >= 0);

_info("Set DTR (PB2) to Low to wake up modem\n");

a64_pio_write(DTR, false);

_info("Status=%d\n", a64_pio_read(STATUS));

_info("Wait 30 ms\n");

up_mdelay(30);

_info("Status=%d\n", a64_pio_read(STATUS));

// Set PB3 to Power On LTE Modem (BB-PWRKEY / PWRKEY).

// PWRKEY should be pulled down at least 500 ms, then pulled up.

#define PWRKEY (P_OUTPUT | PIO_PORT_PIOB | PIO_PIN3)

_info("Configure PWRKEY (PB3) for Output\n");

ret = a64_pio_config(PWRKEY);

DEBUGASSERT(ret >= 0);

_info("Set PWRKEY (PB3) to High\n");

a64_pio_write(PWRKEY, true);

_info("Status=%d\n", a64_pio_read(STATUS));

_info("Wait 600 ms\n");

up_mdelay(600);

_info("Status=%d\n", a64_pio_read(STATUS));

_info("Set PWRKEY (PB3) to Low\n");

a64_pio_write(PWRKEY, false);

_info("Status=%d\n", a64_pio_read(STATUS));

// Set PH8 to High to Enable LTE Modem and Disable Airplane Mode (BB-DISABLE / W_DISABLE#)

#define W_DISABLE (P_OUTPUT | PIO_PORT_PIOH | PIO_PIN8)

_info("Configure W_DISABLE (PH8) for Output\n");

ret = a64_pio_config(W_DISABLE);

DEBUGASSERT(ret >= 0);

_info("Set W_DISABLE (PH8) to High\n");

a64_pio_write(W_DISABLE, true);

_info("Status=%d\n", a64_pio_read(STATUS));

// Poll for Modem Status until it becomes Low

for (int i = 0; i < 30; i++) // Max 1 minute

{

// Read the Modem Status

uint32_t status = a64_pio_read(STATUS);

_info("Status=%d\n", status);

// Stop if Modem Status is Low

if (status == 0) { break; }

// Wait 2 seconds

up_mdelay(2000);

}

// TODO: Read PL6 to handle Ring Indicator / [Unsolicited Result Code](https://embeddedfreak.wordpress.com/2008/08/19/handling-urc-unsolicited-result-code-in-hayes-at-command/)

return OK;

}References:

What's the purpose of the above LTE Modem pins?

Read the article...

From Quectel EG25-G Hardware Design Guide...

Power-on/off

| Pin Name | Pin No. | I/O | Description | DC Characteristics | Comment |

|---|---|---|---|---|---|

| PWRKEY | 21 | DI | Turn on/off the module | VH = 0.8 V | The output voltage is 0.8V because of the diode drop in the Qualcomm chipset. |

| RESET_N | 20 | DI | Reset signal of the module | VIHmax = 2.1 V, VIHmin = 1.3 V, VILmax = 0.5 V | If unused, keep it open. |

-

PWRKEY should be pulled down at least 500 ms, then pulled up

(EG25-G HW Guide, Page 41)

-

"Make sure that VBAT is stable before pulling down PWRKEY pin. It is recommended that the time between powering up VBAT and pulling down PWRKEY pin is no less than 30 ms."

(EG25-G HW Guide, Page 41)

-

"The RESET_N pin can be used to reset the module. The module can be reset by driving RESET_N to a low level voltage for 150–460 ms"

(EG25-G HW Guide, Page 42)

-

Note: RESET_N and PWRKEY are High-Low Inverted when accessed through PinePhone’s GPIO Pins.

Other Interface Pins

| Pin Name | Pin No. | I/O | Description | DC Characteristics | Comment |

|---|---|---|---|---|---|

| W_DISABLE# | 4 | DI | Airplane mode control | VILmin = -0.3 V, VILmax = 0.6 V, VIHmin = 1.2 V, VIHmax = 2.0 V | 1.8 V power domain. Pull-up by default. At low voltage level, module can enter into airplane mode. If unused, keep it open. |

| AP_READY | 2 | DI | Application processor sleep state detection | VILmin = -0.3 V, VILmax = 0.6 V, VIHmin = 1.2 V, VIHmax = 2.0 V | 1.8 V power domain. If unused, keep it open. |

-

"The W_DISABLE# pin is pulled up by default. Driving it to low level will let the module enter airplane mode"

(EG25-G HW Guide, Page 37)

USB Interface

| Pin Name | Pin No. | I/O | Description | DC Characteristics | Comment |

|---|---|---|---|---|---|

| USB_VBUS | 71 | PI | USB connection detection | Vmax = 5.25 V, Vmin = 3.0 V, Vnorm = 5.0 V, Typical: 5.0 V | If unused, keep it open. |

Status Indication

| Pin Name | Pin No. | I/O | Description | DC Characteristics | Comment |

|---|---|---|---|---|---|

| STATUS | 61 | OD | Indicate the module operating status. | The drive current should be less than 0.9 mA | An external pull-up resistor is required. If unused, keep it open. |

-

When PWRKEY is pulled Low, STATUS goes High for ≥2.5 s, then STATUS goes Low

(EG25-G HW Guide, Page 41)

Main UART Interface

| Pin Name | Pin No. | I/O | Description | DC Characteristics | Comment |

|---|---|---|---|---|---|

| RI | 62 | DO | Ring indicator | VOLmax = 0.45 V, VOHmin = 1.35 V | 1.8 V power domain. If unused, keep it open |

Power Supply

| Pin Name | Pin No. | I/O | Description | DC Characteristics | Comment |

|---|---|---|---|---|---|

| VDD_EXT | 7 | PO | Provide 1.8 V for external circuit | Vnorm = 1.8 V, IOmax = 50 mA | Power supply for external GPIO’s pull up circuits. If unused, keep it open. |

I/O Parameters Definition

| Type | Description |

|---|---|

| AI | Analog Input |

| AO | Analog Output |

| DI | Digital Input |

| DO | Digital Output |

| IO | Bidirectional |

| OD | Open Drain |

| PI | Power Input |

| PO | Power Output |

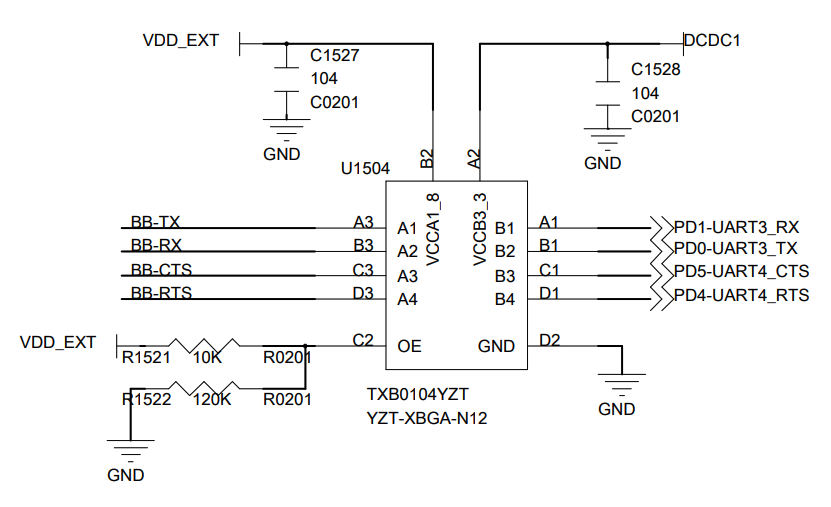

(TXB0104 is a Voltage Translator)

The LTE Modem to connected to PinePhone (Allwinner A64) at these UART Ports (pic above)...

-

A64 Port UART3: RX and TX

-

A64 Port UART4: CTS and RTS

-

A64 Port PB2: DTR

(Default 115.2 kbps, up to 921.6 kbps)

Thus we may check UART3 to see if the LTE Modem responds to AT Commands.

LTE Modem works OK with UART3 on NuttX yay! See the test log here...

Note: Modem UART flow control is broken

"Not resolved in v1.2 -- assumption is that USB will be used for high-bandwidth modem I/O.

BB-TX and BB-RX are connected to UART3 (PD0/PD1). BB-RTS and BB-CTS are connected to UART4 (PD4/PD5). To use hardware flow control, TX/RX would need to be connected to UART4, swapping PD0/PD1 with the motor control and rear camera reset GPIOs at PD2/PD3. This would need a device tree change.

Hardware flow control can be disabled with the AT+IFC command, and USB can also be used for commands instead of the UART. So the impact of this problem is unclear."

Note: Modem PWR_KEY signal resistor population

"Resolved in v1.2 by separating the modem PWRKEY (PB3) and STATUS (PH9) signals.

On the dev phone (1.0) this signal was connected to PB3. This allows for turning on/off the modem via GPIO from a kernel driver. If proper power down is to be implemented in the kernel for the modem, to allow safe shutdown of the modem before turning off the 4g-pwr-bat, kernel has to be able to signal to the modem to shut down and wait 30s. This is not possible on braveheart. Without this signal, kernel can't do anything to shut down the modem, and would have to rely on userspace to properly manage the modem power up/down sequence. Relying on userspace risks users shutting down the modem without proper wait time of 30s, risking modem damage (flash data corruption).

It would be nice to also have access to the STATUS signal from the modem, so that the driver can detect whether the modem is on or off (userspace might have turned modem off already via AT commands). Given that PWR_KEY pulse will either turn the modem on or off, based on the current status, it's necessary to know the current status before sending the pulse.

There's a STATUS signal routed to PWR_KEY on BraveHeart, that keeps the PWRKEY deasserted when the modem is on and it's not possible to pull it up from PB3, even if R1516 would be optionally mounted.

So after powerup you can't change PWR_KEY signal anymore from PB3 even if R1516 is mounted, and it's not possible to turn off the modem via PB3."

TODO: Test LTE Modem with USB. Does the USB Enumeration work?

We're now testing USB CDC ACM on PinePhone, to see if NuttX can enumerate USB Devices correctly.

Select these options in menuconfig...

-

Enable "RTOS Features > Work queue support > Low priority (kernel) worker thread"

Set "Number of low-priority worker threads" to 2

-

Enable "Device Drivers > USB Host Driver Support > USB Hub Support"

And "CDC/ACM Support"

Does the Quectel LTE Modem run on USB CDC ACM?

The lsusb and dmesg logs for PinePhone might be helpful later...

TODO: Get the USB Config File for PinePhone: /etc/udev/rules.d

Why is "Number of low-priority worker threads" set to 2?

Because "CDC/ACM Support" won't compile with the default value of 1.

Earlier we saw this code for setting the USB Magnitude, Rate and Threshold in the USB PHY Driver: sun4i_usb_phy_init

static int sun4i_usb_phy_init(struct phy *phy) {

...

// Assume ID is 1 for Port USB 1

if (usb_phy->id == 0)

sun4i_usb_phy_write(phy, PHY_RES45_CAL_EN,

PHY_RES45_CAL_DATA,

PHY_RES45_CAL_LEN);

/* Adjust PHY's magnitude and rate */

sun4i_usb_phy_write(phy, PHY_TX_AMPLITUDE_TUNE,

PHY_TX_MAGNITUDE | PHY_TX_RATE,

PHY_TX_AMPLITUDE_LEN);

/* Disconnect threshold adjustment */

sun4i_usb_phy_write(phy, PHY_DISCON_TH_SEL,

data->cfg->disc_thresh, PHY_DISCON_TH_LEN);(sun4i_usb_phy_write is defined here)

TODO: Is this needed for NuttX?

Here's the PinePhone USB Controller Configuration in U-Boot Bootloader: phy-sun4i-usb.c

static const struct sun4i_usb_phy_cfg sun50i_a64_cfg = {

.num_phys = 2,

.type = sun50i_a64_phy,

.disc_thresh = 3,

.phyctl_offset = REG_PHYCTL_A33,

.dedicated_clocks = true,

.hci_phy_ctl_clear = PHY_CTL_H3_SIDDQ,

.phy0_dual_route = true,

};(PHY_CTL_H3_SIDDQ is 1 << 1)

TODO

-

USB PHY Power Doc: sun4i-usb-phy.txt

DRAM: 2048 MiB

Trying to boot from MMC1

NOTICE: BL31: v2.2(release):v2.2-904-gf9ea3a629

NOTICE: BL31: Built : 15:32:12, Apr 9 2020

NOTICE: BL31: Detected Allwinner A64/H64/R18 SoC (1689)

NOTICE: BL31: Found U-Boot DTB at 0x4064410, model: PinePhone

NOTICE: PSCI: System suspend is unavailable

U-Boot 2020.07 (Nov 08 2020 - 00:15:12 +0100)

DRAM: 2 GiB

MMC: Device 'mmc@1c11000': seq 1 is in use by 'mmc@1c10000'

mmc@1c0f000: 0, mmc@1c10000: 2, mmc@1c11000: 1

Loading Environment from FAT... *** Warning - bad CRC, using default environment

starting USB...

No working controllers found

Hit any key to stop autoboot: 0

switch to partitions #0, OK

mmc0 is current device

Scanning mmc 0:1...

Found U-Boot script /boot.scr

653 bytes read in 3 ms (211.9 KiB/s)

## Executing script at 4fc00000

gpio: pin 114 (gpio 114) value is 1

359853 bytes read in 21 ms (16.3 MiB/s)

Uncompressed size: 10539008 = 0xA0D000

36162 bytes read in 5 ms (6.9 MiB/s)

1078500 bytes read in 51 ms (20.2 MiB/s)

## Flattened Device Tree blob at 4fa00000

Booting using the fdt blob at 0x4fa00000

Loading Ramdisk to 49ef8000, end 49fff4e4 ... OK

Loading Device Tree to 0000000049eec000, end 0000000049ef7d41 ... OK

Starting kernel ...

pinephone_pmic_init: Set DLDO1 Voltage to 3.3V

pmic_write: reg=0x15, val=0x1a

a64_rsb_write: rt_addr=0x2d, reg_addr=0x15, value=0x1a

pmic_clrsetbits: reg=0x12, clr_mask=0x0, set_mask=0x8

a64_rsb_read: rt_addr=0x2d, reg_addr=0x12

a64_rsb_write: rt_addr=0x2d, reg_addr=0x12, value=0xd9

pinephone_pmic_init: Set LDO Voltage to 3.3V

pmic_write: reg=0x91, val=0x1a

a64_rsb_write: rt_addr=0x2d, reg_addr=0x91, value=0x1a

pinephone_pmic_init: Enable LDO mode on GPIO0

pmic_write: reg=0x90, val=0x3

a64_rsb_write: rt_addr=0x2d, reg_addr=0x90, value=0x3

pinephone_pmic_init: Set DLDO2 Voltage to 1.8V

pmic_write: reg=0x16, val=0xb

a64_rsb_write: rt_addr=0x2d, reg_addr=0x16, value=0xb

pmic_clrsetbits: reg=0x12, clr_mask=0x0, set_mask=0x10

a64_rsb_read: rt_addr=0x2d, reg_addr=0x12

a64_rsb_write: rt_addr=0x2d, reg_addr=0x12, value=0xd9

a64_usbhost_clk_enable: CLK_USB_PHY0

set_bit: 0x1c200cc Bit 8

a64_usbhost_clk_enable: CLK_USB_PHY1

set_bit: 0x1c200cc Bit 9

a64_usbhost_clk_enable: CLK_BUS_OHCI0

set_bit: 0x1c20060 Bit 28

a64_usbhost_clk_enable: CLK_BUS_EHCI0

set_bit: 0x1c20060 Bit 24

a64_usbhost_clk_enable: CLK_USB_OHCI0

set_bit: 0x1c200cc Bit 16

a64_usbhost_clk_enable: CLK_BUS_OHCI1

set_bit: 0x1c20060 Bit 29

a64_usbhost_clk_enable: CLK_BUS_EHCI1

set_bit: 0x1c20060 Bit 25

a64_usbhost_clk_enable: CLK_USB_OHCI1

set_bit: 0x1c200cc Bit 17

a64_usbhost_reset_deassert: RST_USB_PHY0

set_bit: 0x1c200cc Bit 0

a64_usbhost_reset_deassert: RST_USB_PHY1

set_bit: 0x1c200cc Bit 1

a64_usbhost_reset_deassert: RST_BUS_OHCI0

set_bit: 0x1c202c0 Bit 28

a64_usbhost_reset_deassert: RST_BUS_EHCI0

set_bit: 0x1c202c0 Bit 24

a64_usbhost_reset_deassert: RST_BUS_OHCI1

set_bit: 0x1c202c0 Bit 29

a64_usbhost_reset_deassert: RST_BUS_EHCI1

set_bit: 0x1c202c0 Bit 25

a64_usbhost_initialize: TODO: switch off USB bus power

a64_usbhost_initialize: TODO: Setup pins, with power initially off

usbhost_registerclass: Registering class:0x40125838 nids:2

EHCI Initializing EHCI Stack

a64_printreg: 01c1b010<-00000000

a64_printreg: 01c1b014->00001000

a64_printreg: 01c1b010->00000000

a64_printreg: 01c1b010<-00000002

a64_printreg: 01c1b010->00080b00

a64_printreg: 01c1b018<-00000000

a64_printreg: 01c1b014<-0000003f

EHCI HCIVERSION 1.00

a64_printreg: 01c1b004->00001101

EHCI nports=1, HCSPARAMS=1101

a64_printreg: 01c1b008->0000a026

EHCI HCCPARAMS=00a026

a64_printreg: 01c1b028<-40a88fa0

a64_printreg: 01c1b024<-40a99000

a64_printreg: 01c1b010->00080b00

a64_printreg: 01c1b010<-00080b30

a64_printreg: 01c1b010->00080b30

a64_printreg: 01c1b010<-00080b31

a64_printreg: 01c1b050->00000000

a64_printreg: 01c1b050<-00000001

a64_printreg: 01c1b014->00000000

a64_ehci_initialize: irq_attach

a64_printreg: 01c1b018<-00000037

a64_ehci_initialize: up_enable_irq

a64_ehci_initialize: TODO: a64_usbhost_vbusdrive

a64_printreg: 01c1b054->00001000

EHCI USB EHCI Initialized

a64_usbhost_initialize: 1

a64_usbhost_initialize: Status=0

pinephone_pmic_usb_init: Set DCDC1 Voltage to 3.3V

pmic_write: reg=0x20, val=0x11

a64_rsb_write: rt_addr=0x2d, reg_addr=0x20, value=0x11

pmic_clrsetbits: reg=0x10, clr_mask=0x0, set_mask=0x1

a64_rsb_read: rt_addr=0x2d, reg_addr=0x10

a64_rsb_write: rt_addr=0x2d, reg_addr=0x10, value=0x37

a64_usbhost_initialize: Status=0

a64_usbhost_initialize: Wait 1000 ms

a64_usbhost_initialize: Status=0

a64_usbhost_initialize: Configure PWR_BAT (PL7) for Output

a64_usbhost_initialize: Set PWR_BAT (PL7) to High

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Wait 1000 ms

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Configure RESET_N (PC4) for Output

a64_usbhost_initialize: Set RESET_N (PC4) to High

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Configure PWRKEY (PB3) for Output

a64_usbhost_initialize: Set PWRKEY (PB3) to High

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Wait 30 ms for VBAT to be stable

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Set PWRKEY (PB3) to Low

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Wait 500 ms

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Set PWRKEY (PB3) to High

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Configure W_DISABLE (PH8) for Output

a64_usbhost_initialize: Set W_DISABLE (PH8) to High

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Green LED

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Red LED

a64_usbhost_initialize: Status=1

a64_usbhost_initialize: Blue LED

a64_usbhost_initialize: Status=1

nsh: mkfatfs: command not found

e

h

cNuttShell (NSH) NuttX-12.0.3

i

_nsh>waiter: ehci_waiter: Running

a64_wait: Wait for connect / disconnect

nsh> ls

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: mm_heap/mm_malloc.c:200 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x40a8d218 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc8

up_dump_register: x24: 0x400f0277 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a96610

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a96550

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a96490

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a963d0

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a96310

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a96250

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a96190

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a960d0

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a96010

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a95f50

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a95e90

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a95dd0

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a95d10

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a95c50

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a95b90

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a95ad0

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a95a10

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d

up_dump_register: x22: 0x0 x23: 0xc2

up_dump_register: x24: 0x400effd8 x25: 0x40124000

up_dump_register: x26: 0x0 x27: 0x0

up_dump_register: x28: 0x0 x29: 0x0

up_dump_register: x30: 0x4008b1d8

up_dump_register:

up_dump_register: STATUS Registers:

up_dump_register: SPSR: 0x40000005

up_dump_register: ELR: 0x40081000

up_dump_register: SP_EL0: 0x40a96900

up_dump_register: SP_ELX: 0x40a95950

up_dump_register: TPIDR_EL0: 0x40a94608

up_dump_register: TPIDR_EL1: 0x40a94608

up_dump_register: EXE_DEPTH: 0xffffffffffffffff

_assert: Current Version: NuttX 12.0.3 4d922be-dirty Mar 7 2023 15:54:47 arm64

_assert: Assertion failed : at file: misc/lib_mutex.c:194 task: nsh_main 0x4008b230

up_dump_register: stack = 0x4012d660

up_dump_register: x0: 0x4012d660 x1: 0xa

up_dump_register: x2: 0x20 x3: 0x400f2b22

up_dump_register: x4: 0x4a10 x5: 0x0

up_dump_register: x6: 0x4 x7: 0x88

up_dump_register: x8: 0x888 x9: 0x0

up_dump_register: x10: 0x2 x11: 0xa200023

up_dump_register: x12: 0x1c x13: 0x1

up_dump_register: x14: 0x0 x15: 0x1c28000

up_dump_register: x16: 0x4008eb70 x17: 0x1

up_dump_register: x18: 0x0 x19: 0x0

up_dump_register: x20: 0x40a94608 x21: 0x400f292d