-

Notifications

You must be signed in to change notification settings - Fork 7

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Problems with TopLevelGen #3

Comments

|

On line 64 I put the Spinal project inside the source folder of my Xilinx project so I don't have to copy the output file to that project every time. |

|

But there does seem to be a problem with that TopLevel.scala has segdis as 11 bits, but a 4 digit display needs 12 bits - hence the width mismatch error. I was also a bit confused that a parameter called NumberOfDisplays is actually the number minus 1. |

|

For a 2 digit display change line 14 to |

|

Yes, I have changed the code to work for a 2-digit display and that is currently building OK. I probably will make the change to remove the decimal point. I don't think it makes sense to zero reference values such as widths, lengths or the number of elements of something. It only really makes sense for indexes. Is it a Mojo board you are using? I am planning to change the uart to the spinal.lib version and the ram to use Mem. |

|

Yes, I'm using a Mojo V3. When you get it working I would like to see a picture of your setup. |

|

Another thing that would be helpful would be to document which functions (IN, LOAD, RUN, MEM PROTECT) corresponding to switches 8, 9, 10 and 11. I am currently trying to work out which needs to be the button. It is not working yet, but this is what I am thinking of: There is a possibility of using the Oled display for extra information, such as the address. |

|

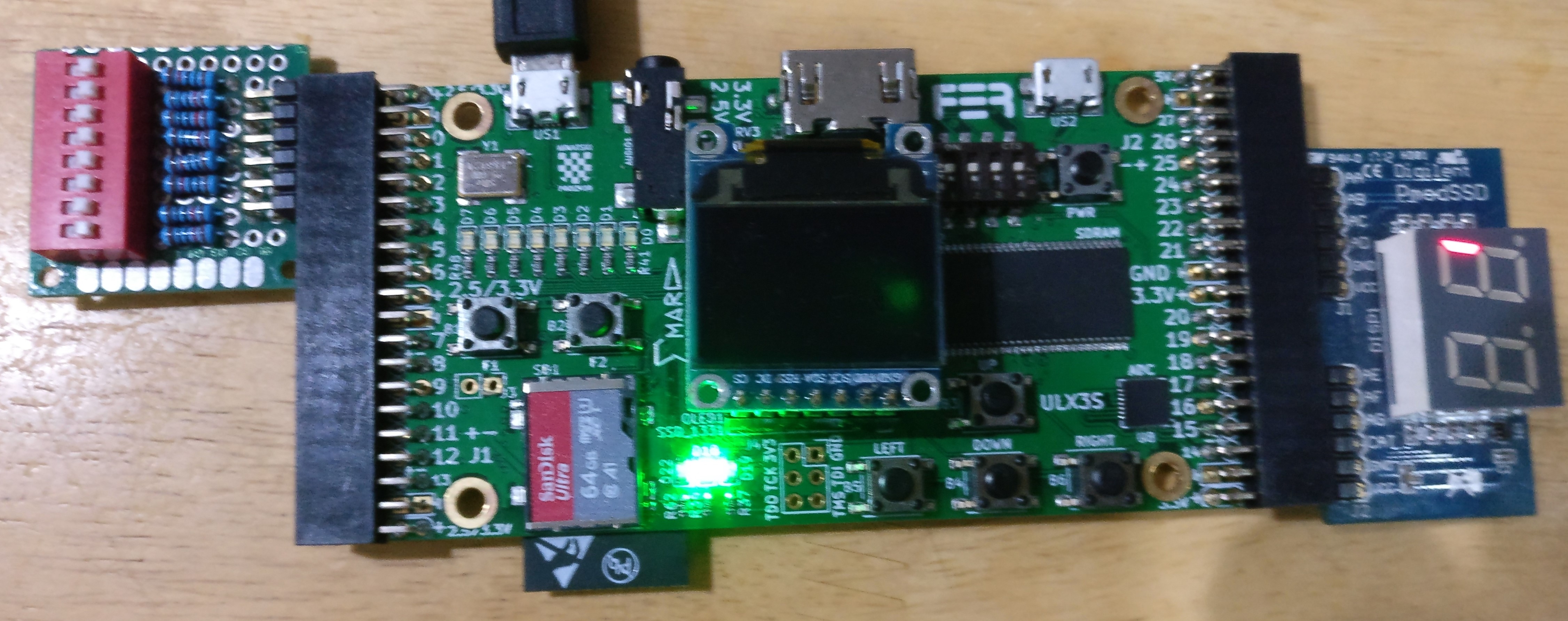

My version seems to be mainly working now. I am not sure about the uart. I have emulated your uart implementation with separate Rx and Tx controllers, but that duplicates some code and it may be better to use a single UartCtrl with the spinal.lib version. Also I probably need to add fifos. Loading data from the Uart seems to reverse the hex digits, but I suspect that is because my port of your seven segment driver has reversed the digits, so I need to look at that. I am not sure how to test the Uart Tx. Your Wait and Clear switches seem to be slightly different to the Run and Load switches I have seen in COSMAC Elf videos, for example - https://www.youtube.com/watch?v=s1H87_xUhOQ - and the combination that resets the address seems to be different. Also you don't seem to have the 1-bit output for the LED. I don't really know anything about the COSMAC ELF other than what is in the Wikipedia article and some youtube videos, so I am not sure how to test if my version is working correctly. My main interest in it is that we have other computers from the same era running on the Ulx3s board, such as the Altair 8800 and the Apple1, and I wanted to add another. Also I want to improve my SpinalHDL skills. My Ulx3s version is at https://github.com/lawrie/FPGACosmacELF |

|

I have corrected the problem I had with the hex digits reversed now. |

|

hmm, after looking at the code I kinda left it in a custom state of playing with stuff. I have been eyeing the Ulx3s board, and I would like to get one but I'm not sure where to go to buy one. |

|

I did try an FPGA implementation of the CHIP-8 CPU on a TinyFPGA BX board using an Oled display and played a few games on it -see https://github.com/lawrie/fpga-chip8 You can ask Goran Mahovlic on the Ulxs3 gitter hub if he has any boards - https://gitter.im/ulx3s/Lobby Or you can email him on ulx3s.fpga@gmail.com He is usually keen to sell boards to developers who get more stuff working on Ulx3s. |

I think I may have fixed the issue with the Run and Load switches, I had a bug in how the Clear flag reset the CPU. |

When I do `sbt "runMain Spinal1802.TopLevelGen" I get a width mismatch error. segdis seems to need to be 12 bits not 11 bits. I am a bit confused about how many seven-segment digits you are using.

On the board I am using I will probably use a 7-segment display PMOD. I have one with 2 digits, and one with 3 digits. How many digits are you currently using. I believe the original Cosmac ELF had just two digits.

I also don't understand why you have targetDirectory = ".." in TopSpinalConfig. What directory are you doing the generation from and what directory do you want it generated in?

The text was updated successfully, but these errors were encountered: