-

Notifications

You must be signed in to change notification settings - Fork 15

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

I have created 3000+ unique balancer network files (5.92 MB) ready for use by Factorio-SAT. Where should I publish them? #14

Comments

|

Probably put these in your own repository uncompressed so people can browse them and download ones they want :) |

|

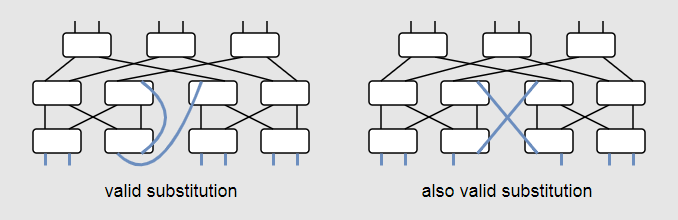

Thanks for taking interest in the project! Probably best to put them in their own repo. If you've found an improved balancer design, then feel free to merge in the improved network. Otherwise this repo is a tool for making balancers. If you have neat algorithm for generating networks, I'd feel comfortable merging that. I'm not sure what you're getting on with in regards to the 2-4, since the one you've provided is just the regular limited throughput one. Maybe I'm looking at the wrong one? At the moment your networks don't make use of "flexible" layouts. This could get you some better performance and reduce the number of network variants needed prove a minimal balancer size. In the existing 6-6 network file in the repo both variants are compatible. The colour 7 is being provided by all 4 final splitters and the loopback connection's only condition is that the colour is 7. Hence the loopback connections can either come from different splitters or the same splitter. |

I can see that the two 6-6 networks are equivalent, where one preferably contains symmetrical subgraphs, but it's hard for me to immediately understand why they should result in equivalent behavior. I don't remember what I did to generate these networks. I even forgot I did so and recently have been trying to solve the problem optimally (minimizing splitters, and now to be preferring extra connections between subgraphs). I also have been considering using deep learning or even deep reinforcement learning to provide an alternative to blueprint generation given balancer networks. In the process of working with these problems over the past couple years, I have constructed a nice framework for dealing with blueprint strings, extracting the balancer graph from a blueprint, constructing and evaluating balancer graphs, modeling the physical belt-by-belt construction of a balancer as a turtle-like environment (showing where the belt "head" can possibly be extended, etc.), and more. I don't put much on GitHub, but these tools of mine could definitely be beneficial to others aspiring to solve similar problems. I am interested in your project because from the very first day (2016) I learned how to balance three belts using splitters, I had the greatest curiosity in my mind, which is to know how to create any M-N balancer, both abstractly as a network/graph and physically in Factorio. It is the most intriguing part of the game for me. That said, I will go to a great extent to solve this problem if I have the set of skills to do so. I could say more about the notable things I've done so far regarding belt balancer mathematics and whatnot, but I'll put that in a repo. Lastly, what I said about my networks being throughout unlimited is likely untrue, as you've found, but it is possibly true for large balancers. I thought for some reason the 2-4 I provided followed that rule, but it definitely wouldn't given the way that I generated the networks (I now remember after writing this how I generated them). I augment an M-N balancer to create a (2M)-(2N) balancer by substituting each splitter with a 4-4 throughout unlimited balancer. However, I tried to make the simplification where the non-throughout unlimited 4-4 balancer is used instead because the first two outputs are being fed to the next 4-4 balancer, meaning that the beginning of each 4-4 balancer is same as the end of each 4-4 balancer. That turns every 4-4 balancer into a throughout unlimited 4-4 balancer except for the deepest ones which don't precede another 4-4 balancer. That was the case for augmenting a 1-2 into a 2-4. It's a simple fix to check for that edge case. |

|

It looks like they're not quite equivalent. Plumbing some test designs into https://github.com/d4rkc0d3r/FactorioSimulation gives an equal min-throughput, but more limited throughput combinations on the variant that pulls from different output splitters. With some fiddling around with the input priorities I think they could be improved on a bit, but modelling that is pretty hard. There's a lot of crossover between balancer blueprint design and PCB layout. Definitely some algorithms there could be applied to balancers. I also think that given the PCB layout problem is NP complete, it's likely that balancers are the same. So I doubt that an AI approach could reliably produce optimal balancers, but being able to make a decent blueprint out of any network would be nice. I don't know much about building networks. Aside from start with a benes and simplify. In principle even if a network is optimal and has the lowest splitter count, it's possible that a more compact balancer could be created by using less optimal network with more splitters. Assuming it significantly improves the belt layout. So I think the ideal is to have all the solving done in a single pass. To avoid having to try enumerate all network variants. |

https://github.com/alegnani/verifactory performs balancer verification using SMT solving, and I have looked together with @alegnani into potentially using it's proofs in Factorio-SAT, but unfortunately right now verifactory is searching for counterexamples for balancing, and that doesn't work for how Factorio-SAT works. |

|

You could use IPASIR-UP to bridge the two projects. Which can designate some SAT literals to be constrained by an external solver. |

I briefly looked into IPASIR-UP, but as far as I understand it, I don't think it would help much for integrating verifactory because verifactory would only be able to tell a global yes/no, which doesn't really let the SAT engine infer single variables. If the check could be broken up into smaller chunks, I think it would be useful, but right now it's just a single yes/no for the entire balancer. I'm slowly rewriting clause construction in a way that I think would be a bit more useful for experimentation, in which I have made a separate cardinality clause type mostly for benchmarking different encodings for it, but it's still far from being ready. |

|

You're probably right, I have not managed to get any kind of decent results out of IPASIR-UP. I had a go a tweaking the cardinality constraint encoding and I didn't find much difference between the encodings in pysat. I think as long as the encoding is arc-consistent, then it's alright. |

networks.zip

Most balancers of the type

m-nwhere1 <= m, n <= 64are included in my files. I would have used Factorio-SAT to create blueprints for a blueprint book and exported that book to a string, but I couldn't even generate a blueprint for a single network because it was taking too long. So, I wish to share the network files so that if anyone wants to use them, they're available.My balancer networks are not optimized to use the fewest number of splitters, but they are at least proven to have no throughput issues when not all of their inputs and outputs are used. For example, a 2-4 balancer that has exactly three splitters has throughput issues when feeding two input belts but using only two output belts that both come from the same splitter. My network file for the 2-4 balancer enables full throughput in that scenario. I think that's called UTU, but I may be mistaken.

Where should I publish the files so that others can make use of them? Separate repository? Would people be able to find that? I'd want them to be easy to find for anyone who's looking for them. Thanks!

I've attached a 2.77 MB compressed file to this issue so that they're at least sitting somewhere for now until it can be published to a better location.

The text was updated successfully, but these errors were encountered: